製作編2

アンプ基板製作の初めに、初段用のdual FETを変換基板実装します。

初段用Dual JFET

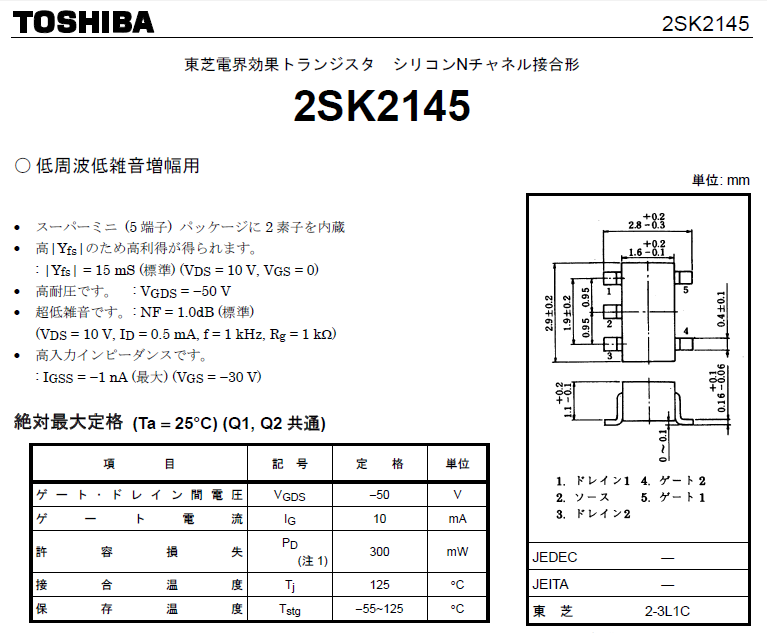

DCアンプの初段に使用するDual JFETについて改めてネットで調べてみました。ありました。同じような事に興味を持って、調査した結果を公開しているページを見つけました。「new_western_elec」の2015年10月4日の記事です。この記事によると、記事公開当時に製造中のDual JFETはこの2SK2145しかないとの事です。特性はすでに生産中止となっている2SK117と同じで、一部特性が違うとのことですが、昨年オーバーホールしたDCパワーアンプの初段に使ったDual JEFT 2SK150相当とのことです。この記事を読んで、2SK2145に対して親近感がわきました。唯一入手可能なこのDual JFETを継続して入手できることを切に願います。

2SK2145GR

Dual JFETは選択の余地がない事が改めて確認できたのでの今回もこれを使用します。チップパッケージの為、DIPへの変換基板と両オスの連結ソケットを使って、DIP用のソケットに実装します。Idss分類は3種類(Y:1.2~3.0mA、GR:2.6~6.5mA、BL:6.0~14.0mA)ありますが、初段のバイアス電流を1mAとしたため、GR品を選択しました。

JFETの実装

変換基板は秋月電子で購入しました。型番はSOT23で10枚で150円です。それでは罰ゲームの時間の始まりです。机に両面テープを貼り、その両面テープにハンダ付けで温度が上がらない部分選び基板を貼りつけて固定します。

基板の片側の3端子用のランドにハンダを付けて、端の1端子を除き吸い取り線でハンダを吸い取ります。端の1端子を他の端子の位置を合わせてハンダ付けします。次に、反対側の2端子をそれぞれハンダ付けします。端子が両端の2本のみなので、こちらの方がやりやすいです。3端子側に戻り、ハンダ多めで残り2端子を固定します。端子間がショートするので、吸い取り線で余分なハンダを吸い取ります。続いて実装確認をします。ソースと2つのドレイン端子間を基板のスルーホール部分で抵抗値を測定します。約100Ω~1KΩくらいであれば正しく接続されています。抵抗値がそれよりも高い場合は、もう1度ハンダをやり直します。ゲート側は、連結ソケット用のスルーホールとチップの足の間の抵抗値を測定します。0Ω近い値であれば問題ありません。

連結ソケット接続

変換基板をDIP用ソケットに差し込む為の足となります。BTL DCパワーアンプ製作時は、連結ソケットを目一杯変換基板に差し込み部品実装面上に連結ソケットの足が立ち上がっていましたが、チップの実装修理時に連結ソケットの足がハンダ処理のじゃまになるため、今回は差し込みを浅くしました。

ハンダ付けの際には、チップ基板実装時と同様に熱を加えない端子を両面テープで固定してハンダ付けをしました。

実装の確認

正しく実装されていることを確認するために、それぞれのJFETのIdssの測定を行います。トランジスタ選別で使用したジグに、8pinDIPのソケットが実装されているので、それを利用して測定します。測定回路は以下のとおりです。

各基板のそれぞれ2回路を1回路づつ測定していきます。

測定結果は以下のとおりです。Idss自体のばらつきはあるものの、Dualの2回路間のばらつきはほとんどありませんでした。4個ともに正しく実装ができていることが確認できたため、No.1,2とNo.3,4をそれぞれのチャンネルで使用することとします。

次回は電源回路から実装スタートします。

つづく(製作編3)